Imagem 1

Entre os anos 1970 e início dos anos 1990 as interfaces seriais não recebiam tanta atenção, já que haviam limitações para altas frequências de sinal e um barramento paralelo parecia ser a saída. Ainda não era a hora certa de uma conexão serial chegar ao estrelato, reinando quase absoluto (o RS-232 teve seu espaço :v) as interfaces paralelas.

Assim, no centro dos holofotes por anos a fio, o barramento ISA (Industry Standard Architecture) surgiu e recebeu várias novas revisões de projeto até ficar insustentável, gerando gargalo nos computadores. O VLB, outra conexão paralela, o substituiu, mas atingindo seus limites tempos depois.

Nisso, a Intel traz ao mercado aquele que talvez seja o barramento mais famoso: o PCI (Peripheral Component Interconnect - Interconexão de Componentes Periféricos). Outras empresas se juntam à Intel afim de aperfeiçoar a tecnologia e torna-la mais popular, criando assim o PCI-SIG (PCI Special Interest Group, que significa "Grupo de Interesse Especial PCI"). A partir daí foi criado o padrão PCI-X (Peripheral Component Interconnect eXtended - Interconexão de Componentes Periféricos Estendida), que era uma versão do slot PCI com clocks mais altos e maior largura do barramento.

O slot PCI e PCI-X, quando foram lançados, acompanharam o desempenho do restante do hardware que era desenvolvido na época. Eles eram utilizados para vários fins (instalação de placas de áudio, rede, captura de vídeo, placas de vídeo, etc). Após alguns anos, quando os jogos de computador estavam começando a ficar mais bem trabalhados e populares e quando os processadores e memórias ganharam mais desempenho, este barramento se mostrou lento e pouco proveitoso, principalmente para a instalação de placas gráficas.

Mesmo assim, o PCI serviu de base para a PCI-SIG trazer ao mercado aquele que ficou exclusivo para placas de vídeo por uns bons anos: o AGP (Accelerated Graphics Port).

O AGP era outro barramento, e com um desempenho até bem avançado, mas que também chegou no seu limite. As GPUs evoluíam muito depressa. Já prevendo essa evolução imparável e necessária, o PCI-SIG criou o atemporal (pelo menos até o momento) PCI Express, que apenas têm de semelhança o nome, sendo completamente diferente do PCI legado.

→ Para saber mais sobre o barramento ISA e eISA, CLIQUE AQUI!

→ Para saber mais sobre o barramento VLB, CLIQUE AQUI!

→ Para saber mais sobre o barramento PCI e PCI-X, CLIQUE AQUI!

→ Para saber mais sobre o barramento AGP, CLIQUE AQUI!

O PCI Express, abreviado por "PCIe", é o foco deste artigo!

O PCI Express adota uma concepção completamente diferente, abandonando as várias trilhas de dados em paralelo que interligam vários dispositivos (o que configura um barramento) em prol de um sistema de conexão serial ponto-a-ponto operando em altas frequências, extremamente modular e de multi-aplicação.

Imagem 2 - Logotipo do padrão PCI Express

Desde que surgiu, em 2003, o PCI-SIG tem atualizado constantemente a interface, como podemos ver na imagem abaixo:

Tabela 1 - As versões do PCI Express e suas principais características

Aqui, devemos começar explicando o conceito de "lane".

Um lane pode ser definido como uma dupla de pares de cancelamento com sinalização de baixa voltagem (LVDS) que operam em modo Full-Duplex, isto é, dois dispositivos podem trocar informações simultaneamente, com menor consumo de energia e redução de EMI.

Tabela 2 - Observe a linha destacada em vermelho

Mas o que seria um par de cancelamento com sinalização de baixa voltagem? Isto pode ser entendido perfeitamente lendo o artigo do HC dedicado ao assunto:

Propaganda de conteúdo relacionado - Clique na imagem acima para abrir este glorioso artigo do HC em uma nova aba!

Para esta conexão Half-Duplex, temos um par para envio de informações (TX_p e TX_n) e um par para recebimento de informações (RX_p e RX_n). Ao juntar 16 lanes, por exemplo, temos uma conexão PCI Express x16, que dá um total de 64 trilhas dedicadas apenas pra transmissão de dados.

Uma conexão PCI Express x1, significa que possui apenas 1 lane (4 trilhas). O mesmo acontece com o slot PCIe x2, x4, x8, e x32. Pode ser utilizado o termo "bit", já que cada par diferencial pode receber ou enviar 1 pulso elétrico e seu sinal invertido por cada lane, portanto, se você ouvir que "um slot PCI Express x16 transmite 16 bits", está correto.

Os domínios de Clock

Uma arquitetura de temporização síncrona é onde uma fonte de clock comum fornece um clock para todos os dispositivos conectados, e esse clock é usado para permitir que os transceptores do dispositivo façam o clock de entrada e saída de dados. Este esquema requer que os clocks cheguem a cada dispositivo precisamente ao mesmo tempo. Há uma quantidade muito pequena de desvio pino-a-pino permitido, o que significa que os comprimentos das trilhas para sinal de clock devem ser combinados para minimizar a quantidade de desvio entre os dispositivos.

Agora torna-se evidente que, à medida que a velocidade do clock aumenta, a defasagem pino-a-pino permitida deve diminuir, o que exige que o roteamento combinado desses rastreamentos de clock se torne cada vez mais preciso.

Uma "arquitetura de temporização síncrona de origem" é onde os dados e o clock são transmitidos pelo dispositivo de origem. Isso significa que não há um clock comum que todos os dispositivos conectados devem usar para travar a entrada e saída de dados. Em vez disso, um dispositivo de transmissão encaminha o clock usado para transmitir os dados e o receptor pegará esse sinal encaminhado para travar os dados transmitidos.

É este sistema que o PCIe incorpora. Ele emprega um esquema em que o clock é “incorporado” no fluxo de dados através da codificação 8B/10B ou 128B/130B. O Clock Data Recovery é a tecnologia utilizada pelo receptor para "capturar" este clock inserido nos dados.

CURIOSIDADE: Devido ao sistema de codificação dos dados, a taxa de transferência é diferente do normal. Você verá na PARTE 2 deste texto os sistemas de codificação de dados do PCIe. Para a revisão 1.0 e 2.0 era utilizada a codificação 8B/10B, onde cada conjunto de 8 bits é transformado em um pacote de 10 bits. Esses 2 bits extras são apenas utilizados para codificação, representando 20% da taxa de transferência.

Numa conexão PCIe x1 1.0 por exemplo, em vez de ser 312,5 MB/s de taxa de transferência, como é perdido 20% com os dados da codificação, ele é padronizado com 250MB/s. Já a revisão 3.0 e 4.0 utilizam a codificação 128B/130B e por este motivo foi possível dobrar a taxa de transferência de dados sem dobrar a frequência (GHz).

Para entender tudo isso melhor, CLIQUE AQUI e veja a PARTE 2!

Esse mecanismo de codificação garante que o fluxo de dados tenha um número suficiente de transições de 0 para 1 e de 1 para 0 para permitir que o clock seja recuperado no lado receptor com o uso de um Phase-Locked Loop (PLL). Com essa arquitetura de temporização, não há mais o problema de rotear cuidadosamente o mesmo relógio para cada dispositivo com quantidades muito pequenas de distorção. No entanto, surge um problema diferente. Cada dispositivo agora tem pelo menos dois domínios de relógio:

→ O domínio de clock local que ele usa para cronometrar todas os seus circuitos internos e transmitir dados;

→ O domínio de clock recuperado (ou recebido) que ele usa para travar dados de entrada.

Diagrama 1 - Os domínios de clock

Os dados que estão sendo recebidos terão que cruzar o "Domínio do Relógio Recuperado" para o "Domínio do Relógio Local" para que o dispositivo processe essas informações. Os Elastic Buffers são implementados em dispositivos PCI Express exatamente para esse propósito, para permitir que os dados recebidos façam a transição do Domínio do Relógio Recuperado para o Domínio do Relógio Local.

Agora, precisamos entender o nível de defasagem de frequência entre uma porta PCIe do emissor e uma porta PCIe do receptor.

A cada pulso de clock é transmitido 1 dado (1 bit). No caso de um slot PCIe x1 1.0, há apenas 1 lane transmitindo a no máximo 2,5 GHz (2,5 bilhões de pulsos por segundo), o que dá uma taxa de transferência teórica de 250 Mega Bytes por segundo (MB/s). Só que há poréns...

CURIOSIDADE: Para calcular a taxa de transferência de dados, e se você não entende muito bem sobre bits, Bytes e clock, leia os artigos sobre estes assuntos para saber mais. Eles já estão disponíveis no site e para acessa-los, clique aqui!

Seguindo o parágrafo que veio antes da curiosidade destacada, todos os dispositivos PCI Express de primeira geração então devem transmitir dados a uma taxa de 2,5 Gbps (Giga-bits por segundo) com tolerância de +/- 300 ppm (partes por milhão). Isso se traduz em uma faixa de frequência permitida de 2,49925 GHz ~ 2,50075 GHz no transmissor de um dispositivo. Devido essa tolerância permitida, dois dispositivos conectados um ao outro podem (e provavelmente estarão) rodando em frequências ligeiramente diferentes. É exatamente isso que vai criar os tais dois domínios de clock dentro de um dispositivo, pelos quais os dados recebidos devem fazer a transição.

Para saber mais sobre clock, conexões síncronas e assíncronas, clique aqui!

OBSERVAÇÃO: Note que, numa conexão síncrona há o RefClk de 100 Mhz, que serve para facilitar o sincronismo dos domínios locais de emissor e receptor, isso reduz a defasagem para +/- 300 ppm. Você verá na sequência deste texto que os esquemas de transmissão completamente assíncrona (isto é, sem o RefClk de 100 Mhz) sofrem mais com essa defasagem e podem atingir valores de + 300 a - 2800 ppm, já que os domínios locais operam de maneira 100% independente.

Elastic Buffer

Com isso, entra no jogo o chamado Elastic Buffer, cuja função é conectar esses dois domínios de clock compensando suas diferenças de fase e frequência, permitindo assim que os dados recebidos mantenham sua integridade à medida que fluem upstream no dispositivo de destino.

A ponte entre esses dois domínios de clock é realizada depositando os dados recebidos no buffer e recuperando o sinal de clock através deles. Após, retira-se os dados do buffer usando o outro domínio de clock (o clock local do dispositivo). Como esses dois domínios de clock podem ser executados em frequências diferentes, o buffer tem o potencial de overflow ou underflow. No entanto, essas condições de erro são evitadas projetando o buffer para monitorar seu próprio estado (ou nível de preenchimento) e permitindo que ele insira ou remova símbolos especiais na taxa apropriada, tornando-o elástico (daí o nome, Elastic Buffer).

O PCI Express define esses símbolos especiais que podem ser inseridos ou removidos como "símbolos SKP" (de "Skip", ou seja, "pulo") que são encontrados apenas em Conjuntos Ordenados SKP (SKP OS). Um conjunto ordenado SKP transmitido é composto por um único símbolo COMMA (vírgula) seguido por três símbolos SKP. Os transmissores são obrigados a enviar conjuntos ordenados SKP periodicamente pelo motivo exato que acabamos de discutir: para evitar uma condição de overflow ou underflow no Elastic Buffer.

CURIOSIDADE: Haverá casos em que um dispositivo não poderá transmitir um conjunto ordenado SKP dentro do intervalo definido de 1180 ~ 1538 símbolos por vez. Isso ocorre durante a transmissão de um grande pacote de camada de transação (TLP), que impede que o dispositivo envie um conjunto ordenado de SKP no horário programado regularmente. Uma vez que o dispositivo não pode interromper a transmissão, ele deve esperar até que todo o TLP seja transmitido para então poder transmitir o(s) conjunto(s) ordenado(s) de SKP atrasado(s).

Durante a grande transmissão TLP, vários deslocamentos de símbolo podem ocorrer no receptor entre o Domínio de Relógio Recuperado e o Domínio de Relógio Local. Para garantir que o Elastic Buffer no dispositivo de destino receba conjuntos ordenados de SKP suficientes para compensar os deslocamentos de vários símbolos, os conjuntos ordenados de SKP que foram programados para transmissão durante o TLP são acumulados. Esses conjuntos ordenados de SKP acumulados são enviados consecutivamente, imediatamente após o término do TLP.

Resumindo: O Elastic Buffer realiza a compensação de tolerância de clock (ponte de domínios de clock) no nível de símbolo e não no nível de bit. O bloco lógico que gera símbolos válidos do fluxo de bits recebido é o Deserializador. Portanto, os dados recebidos devem passar pelo Deserializador antes de serem depositados no Elastic Buffer.

Voltando ao assunto principal deste tópico, a modularidade do PCI Express permite que a conexão seja síncrona ou assíncrona (com ou sem o RefClk de 100 Mhz), dependendo da aplicação.

Um detalhe importante, é que o PCI Express com conexão síncrona aplica apenas um clock de referência por um par diferencial dedicado entre os dispositivos que estão se comunicando. A frequência de operação do circuito, isto é, o clock de referência multiplicado por um circuito PLL é feito internamente, nos controladores PCIe.

Sistema síncrono - Clock Comum

A arquitetura RefClk comum utiliza os mesmos 100 Mhz de referência para ambos os dispositivos que estão se comunicando (Root-Complex / Endpoint ~ Switch) e, portanto, não apresenta nenhuma diferença no clock entre os componentes PCIe. Observe a ilustração:

Diagrama 2 - O clock comum

A frequência de operação do circuito, isto é, o clock de referência multiplicado por um circuito PLL é feito internamente, nos controladores PCIe.

Para um sistema que pode atingir 2,5 Ghz (PCIe revisão 1.0) faz-se necessário multiplicar os 100 Mhz entre 1 e 25 vezes. O PLL faz uma multiplicação dinâmica, isto é, de acordo com a quantidade de dados a ser transferida, portanto, não mantendo o clock máximo o tempo todo.

Por exemplo, quando você está com seu PC ocioso, sua RTX 3080 não vai estar necessariamente na configuração x16 4.0, mas sim poderá estar na configuração PCIe x16 1.0. :v

Sistema assíncrono - Clock independente

Aqui, cada dispositivo PCIe gera seu próprio clock de referência, também padronizado em 100 Mhz.

Nesta modalidade, existem duas variações que podem ser implementadas:

→ RefClk Separado sem Spread Spectrum (SRNS);

→ Ou RefClk Separado com Independent Spread Spectrum Clock (SRIS).

Gerando seu prórpio clock de referência, o PLL o multiplica, gerando um domínio local de clock, no entanto, ele também monitora a frequência dos dados que são recebidos (recupera o clock), fazendo-se necessário ainda mais o Elastic Buffer. Você verá isto na sequência...

Mas o que seria Spread Spectrum?

Spread Spectrum é uma técnica de codificação para a transmissão digital de sinais. Ela foi originalmente desenvolvida pelos militares durante a Segunda Guerra Mundial, com o objetivo de transformar as informações a serem transmitidas num sinal parecido com um ruído radioelétrico evitando assim a monitoração pelas forças inimigas.

A técnica de spread spectrum consiste em codificar e modificar o sinal de informação executando o seu espalhamento no espectro de freqüências. O sinal espalhado ocupa uma banda maior que a informação original, porém possui baixa densidade de potência e, portanto, apresenta uma baixa relação sinal/ruído.

Em outras palavras, basicamente, toda a informação é codificada e transmitida em pacotes em diversas frequências. Essa codificação é transmitida ao receptor e esse seria o único a entender esse código.

Imagem 3 - Fazendo uma analogia com o Spread Spectrum

Como dito acima, o sinal é codificado e somente o receptor “entende” o código transmitido, ou seja, todo e qualquer sinal transmitido que não for compatível com o sinal enviado pelo emissor será tratado como ruído, como interferência e é eliminado pelo receptor, melhorando assim a relação entre o sinal e o ruído do sistema, com isso temos grandes distâncias entre o receptor e o transmissor.

No caso de placas de computador, a temporização de espectro espalhado faz com que o circuito de regulação do sinal varie ligeiramente a frequência em torno do clock alvo, efetivamente "espalhando" a potência por uma banda de frequência um pouco maior.

Numa conexão de dados, o clock de referência é utilizado para gerar o clock final dos controladores, que ditará sua velocidade de operação e taxas de transferências, então, aplicando o Spread Spectrum na geração de clock, implicará em pacotes de dados sendo transmitidos numa faixa de frequência mais ampla, distribuindo a potência, reduzindo EMI.

CURIOSIDADE: O Spread Spectrum é utilizado não só no PCIe, mas sim em outros sistemas de uma placa-mãe de computador, como por exemplo no clock do FSB (Front Side Bus) das placas mais antigas...

Imagem 4 - O BIOS com algumas configurações de Spread Spectrum

Como você pode imaginar, mesmo a menor variação em um sinal de clock pode ser suficiente para criar erros de transferência de dados. Dentro dos parâmetros originais do projeto, a oscilação de clock pode funcionar de maneira possitiva a evitar ruídos e maximizar o desempenho, no entanto, os fundamentos do overclocking exigem o sinal mais limpo, estável e puro possível, e é por isso que o Spread Spectrum deve sempre ser desabilitado neste caso.

Voltando ao assunto Clock, um resumo do que foi descrito nesse tópico:

Diagrama 3 - Os modos síncrono e assíncrono permitidos pelo PCIe

O Data Retiming Section (CDR), inclui uma função de filtro passa-baixa em ambas as arquiteturas de temporização. O filtro CDR rastreará baixa

frequências, fornecendo alinhamento correto do clock e dos dados, no entanto, as altas frequências passarão se predominantes causarem o 'fechamento dos olhos'.

No esquema SRNS / SRIS os clocks de referência são independentes uns dos outros e seu jitter dominante é aleatório, então, seu impacto combinado no sistema é a raiz quadrada da soma dos termos individuais, resultando em maior jitter geral - potencialmente exigindo soluções de ruído de clock mais baixas. O SRNS / SRIS também precisará corrigir as diferenças na precisão do clock entre os lados de transmissão e recepção, o que pode potencialmente degradar o desempenho da latência. A vantagem da desta metodologia é que ela elimina o par diferencial de RefClk no feixe de fios (ou trilhas) que interligam os dispositivos PCIe, simplificando esta parte do projeto.

O SRIS pode ser implementado no clock de referência PCIe com uma taxa de modulação de espectro de dispersão de 30 a 33 kHz e tolerância de desvio entre 0% e -0,5% (comumente conhecido como Spread Spectrum Clock - SSC - que traduzido significa "clock de espectro de dispersão"). O clock modulado normalmente acaba numa onda 'triangular'. Reiterando, a energia total permanece inalterada, mas a potência de pico é reduzida transmitindo os dados numa faixa de frequências maior.

CURIOSIDADE: O protocolo PCIe possui SKP OS (Conjuntos Ordenados Skip) que são usados para compensar as diferenças de frequências entre as taxas de bits nas duas extremidades de um Link. O sub-bloco lógico Receiver Physical Layer deve incluir buffers elásticos que realizam essa compensação. O intervalo entre as transmissões do Conjunto Ordenado SKP é derivado do valor absoluto das diferenças de frequência do clock de Transmissão e Recepção.

O tamanho do buffer elástico é uma preocupação ao operar com a arquitetura de clock SRIS, pois pode precisar de mais entradas em seus buffers elásticos em comparação com os designs que suportam apenas SRNS, o que resulta em latência extra. Este requisito leva em consideração o tempo extra que pode levar para agendar um Conjunto Ordenado SKP se este cair imediatamente após um pacote de tamanho máximo de carga útil.

O "Olho do Sinal" e a Redução da Diafonia

Note que, anteriormente, escrevi "fechamento dos olhos". Mas que diabos seria isto? Uma tradução errada?

Gráfico 1 - O olho do sinal transmitido no PCIe

É possível notar em muitas placas que algumas trilhas se apresentam em zigue-zague, pois é necessário que os dados distribuídos no barramento cheguem ao mesmo tempo no receptor:

Imagem 5 - Trilhas com o mesmo comprimento para facilitar um recebimento alinhado2 no receptor

Com a introdução do Clock Data Recovery (CDR, a recupeção do clock inserido nos dados mencionada no tópico "Sincronismo") e de outras tecnologias, o comprimento de cada trilha pode variar, excluíndo aquele monte de zigue-zague que provocava bastante diafonia (CrossTalk) e prejudicava o olho do sinal.

Um link PCI Express pode ser composto de vários lanes. O dispositivo de transmissão entrega pedaços de um pacote em todas essas pistas ao mesmo tempo (por byte striping do pacote em todas as pistas). No entanto, o dispositivo receptor na outra extremidade do link pode não receber os dados em cada pista exatamente ao mesmo tempo devido à variação de comprimentos para as diferentes pistas entre os dois dispositivos, ou possivelmente devido a algumas outras características de construção da PCB.

OBSERVAÇÃO: Obviamente um par diferencial precisa ter o mesmo comprimento nos dois condutores, afinal o sinal é espelhado e precisa estar sincronizado para reduzir EMI. Isso significa que pequenos zigue-zagues ainda podem ser encontrados nos circuitos!

A diferença de tempo para chegada de dados através das pistas é conhecida como "desvio de pista para pista", e é limitada em 20 / 8 / 6 nanosegundos para 2,5 / 5 / 8 GT/s para que os buffers de hardware possam realinhar os dados distribuídos. Veja o gráfico abaixo:

Gráfico 2 - O recebimento de dados se torna desalinhado entre lanes

→ Cada pista é ligada numa porta do receptor, e cada porta deve deve recuperar o clock do fluxo de dados que chega nessa pista.

→ Cada um desses clocks recuperados deve ter a mesma frequência (pois todos estão travados na frequência de transmissão), porém, devido a atrasos de emissor e comprimento de trilhas, eles podem ter fases diferentes entre si.

Essas fases podem estar até mais de 360° defasadas uma em relação à outra. Para corrigir isso, entra em jogo o Deskew.

O objetivo do sistema Deskew é realinhar as fases dos dados recebidos de forma eficaz. Esse processo pode ser realizado inteiramente de forma digital em duas etapas simples. O primeiro passo é travar os símbolos em todos as pistas com um clock comum (um dos clocks recuperados pode ser utilizado como referência para todas as outras pistas). Isso alinha os símbolos recebidos nos limites de clock. Eles ainda podem estar fora de fase um em relação ao outro, mas agora estão fora de fase em incrementos de 360° (ciclos de clock). Veja o gráfico abaixo:

Gráfico 3 - Como fica após o alinhamento

Neste ponto, os símbolos estão todos deslocados, porém, razoávelmente sincronos (suas diferenças de fase estão agora em incrementos de clocks), então, o segundo passo do procedimento de assimetria é simplesmente atrasar as faixas “mais rápidas” pelo valor apropriado. Agora sim, os dados foram alinhados em todas as faixas para que o receptor processe essas informações.

CURIOSIDADE: Se essa correção fosse tentada no domínio analógico, isso envolveria ter que deslocar as informações recebidas por frações de clock, tornando-se muito complicado de se implementar.

Para ter uma noção maior do que estudamos até agora sobre PCIe, vamos analizar um bloco de hardware PHY de um controlador PCIe:

Diagrama 4 - O bloco de hardware "PHY" em detalhes

OBSERVAÇÃO: Para saber mais sobre os blocos de hardware que compõem um controlador PCIe, veja a PARTE 2 deste texto, já linkada aqui anteriormente.

Analisamos:

→ Note a entrada de dados do lane (RX_P e RX-N) e o sistema de recuperação do sinal de clock através do CDR e um PLL;

→ Perceba que os dados necessitam passar por um SerDes para que, numa conexão paralela de 10 bits de largura sejam alocados no Elastic Buffer;

→ Tanto o SerDes quanto o buffer elástico precisam de um detector de vírgula (COMMA, um símbolo do tipo K28.5 neste caso). O SerDes para poder se situar nos dados (o alinhamento dos dados para ele ainda é aleatório), e o Elastic Buffer para identificar os símbolos Skip e retira-los de acordo com o domínio de clock local;

→ Há um pequeno FIFO (Register) e o sistema decodificador, que neste caso é 8B/10B, pois se trata de um controlador de um chip da Nexperia com PCIe rev.1.0.

Entendendo isto, vamos para um outro tópico importante:

Seja uma conexão entre chips na mesma PCB ou chips em PCBs diferentes ligadas através de Conectores Eletromecânicos (abreviado por CEM, mas conhecido popularmente como "slot") ou cabos, há a necessidade da padronização até mesmo dos limites de ruído, que é o que geram perdas:

Tabela 3 - Padronização dos limites de ruído no PCIe

A perda de inserção é a perda de potência do sinal resultante da inserção de um dispositivo em uma linha de transmissão, e este valor é expresso e deciBel (dB), uma unidade de medida padrão do SI utilizada em geral para medir a intensidade relativa de um sinal.

No PCIe 5.0 os efeitos da temperatura / umidade podem resultar em

± 10% de variação na perda de inserção para materiais de PCB de alta qualidade e até ± 25% de variação para materiis comuns (FR-4 de qualidade inferior).

RX_Margining

Note que, a evolução do PCIe 3.0 para o 4.0 foi bastante demorada. Necessitou-se de 7 anos de estudos para lançar uma interface com o dobro de desempenho mantendo a retro compatibilidade com as versões anteriores desta plataforma. Este tempo longo foi por causa das barreiras físicas cada vez mais eminentes nesta busca desenfreada por aumento da taxa de transferência:

→ Atenuação de sinal causados pelos materiais que compõem as PCBs, bem como suas espessuras e tamanhos;

→ Atenuação de sinal causados pelo dimensionamento de trilhas ou fios (comprimento, largura / espessura e espaçamento entre linhas);

→ Atenuação de sinal causados pelas condições ambientais (absorção de umidade, principalmente).

O PCI Express, uma interconexão ponto a ponto, suporta conectividade interna e externa através de um conjunto de cabos ou no nível da placa. Três casos comuns de interconexão no nível da placa são:

→ Chip-a-chip (sem conectores);

→ Uma interface de expansão com uma placa e um conector;

→ e um backplane com várias placas e conectores.

Em um backplane complexo, há muitas razões pelas quais a integridade do sinal pode degradar, incluindo cross-talk (diafonia), reflexão, descontinuidades e perda de canal.

O próximo gráfico mostra um exemplo de diferenças de perda de canal em uma placa de circuito impresso (PCB) de FR-4, onde um traço de 24 polegadas tem uma perda muito maior numa conexão PCIe 4.0 x16 do que em uma PCIe 3.0 x16.

Gráfico 4 - Perdas de canal tendem a ser maiores no PCIe 4.0

Devido às variações de fabricação do PCB e do conector, um cartão em um slot pode ter um desempenho de sinal diferente em comparação com um cartão de uma fabricante diferente montado em outro slot, conforme mostrado na próxima imagem:

Imagem 6 - Diferenças na qualidade de placxas de expansão influenciam no desempenho final do sistema

Perceba na imagem acima um olho de sinal mais ruidoso no Slot 5 e um olho de sinal mais limpo no Slot 2.

Variações de fabricação do PCB, como espessura da camada da placa, largura da trilha ou o espaçamento entre elas pode aumentar a perda de canal, impedâncias e ruído do sistema. Qualquer um ou todos eles podem afetar a qualidade e o tamanho da abertura do olho do sinal. Essas variações de PCB podem ser vistas tanto de fornecedor para fornecedor quanto de lote para lote do mesmo fabricante.

Sabemos que, em geral, o material das PCBs é FR4 (resina de poliepoxido reforçado com tecido de lã de vidro). A questão aqui é que, existem sérios fatores que influem no desempenho de uma conexão de dados de alta taxa de transferência entre circuitos de uma placa, entre eles a absorção de umidade pelo substrato e a espessura das camadas, bem como a deposição do Cobre que forma as trilhas (quantidade, largura e espessura de traço e rugosidade).

Não existe uma definição padrão da indústria de perda média, perda baixa e perda ultrabaixa, de modo que o projetista deve avaliar os valores e saber definir quando são demasiado altos.

Tabela 4 - As trilhas (Striplines / Microstrip Traces) também possuem seus limites

A margem do lane no receptor é um recurso obrigatório para todas as conexões de revisão 4.0, onde o controlador PCIe obtém informações de margem do receptor PHY, enquanto opera no modo ativo (estado do link L0) a uma taxa de dados de 16 GT/s, sem a necessidade de qualquer hardware externo. Usando os recursos de controle de margem da pista e relatório de erros, o controlador determina a margem em cada pista PCIe do sistema avaliando a largura do olho do receptor (tempo) e a altura do olho (amplitude do sinal – tensão). Isso permite uma avaliação eficiente da margem do sistema no dispositivo PCIe sem a necessidade de qualquer configuração adicional.

A implementação real do recurso de margem no controlador é específica do projeto:

→ Alguns projetos utilizam dados ou amostras de erro no PHY para fazer e avaliar o relatório das informações do olho do sinal;

→ e outros podem optar por simplesmente estressar o olho injetando uma quantidade apropriada de jitter nos dados.

A avaliação de margem dos dados fornecidos pelo PHY também pode ser processada de forma diferente pelo controlador. Os controladores podem usar diferentes deslocamentos, etapas de tensão e tempo para diferentes níveis de granularidade de coleta de dados. Além disso, diferentes tolerâncias de erro de bit podem ser definidas antes de sair da avaliação de margem.

Como exemplo no próximo gráfico, a margem de lane pode ser implementada partindo de um ponto da amostra do olho, e em etapas incrementais, sua largura pode ser escaneada para a direita e para a esquerda para verificar a margem mínima. Opcionalmente, a altura do olho pode ser escaneada do mesmo ponto da amostra até a parte superior e inferior, para obter sua margem mínima também.

O controlador, usando as informações de margem do PHY, identifica onde ocorre a falha no sistema e determina a margem do lane. Abaixo, o exemplo de um olho receptor a 16 GT/s (PCIe 4.0) em uma posição ideal com amplas margens de sinal além da largura e altura mínimas:

Gráfico 5 - Um olho de sinal ideal no receptor para o PCIe

RX e TX_EQ

É a equalização de transceiver, que descreve o handshaking entre os dispositivos que vão começar a se comunicar entre si.

Handshake, ou “aperto de mão” é o processo pelo qual duas ou mais máquinas afirmam que reconheceram umas às outras e estão prontas para iniciar a comunicação. O handshake é utilizado em protocolos de comunicação, tais como: FTP, TCP, HTTP, SMB, SMTP, POP3 etc. Um dos parâmetros que devem ser negociados no handshaking é justamente a velocidade de comunicação, que no PCI Express varia entre as versões 1.0, 2.0, 3.0, 4.0 e 5.0.

Neste caso (PCIe 4.0), para haver um "aperto de mão" entre emissor e transmissor é de fundamental importância que o sistema conheça a margem dos lanes que vão compor a conexão.

A partir do PCIe 3.0, a equalização também é definida por um novo equalizador comportamental aplicado no receptor e denominado CLTE (Continuous-Time Linear Equalizer, ou "Equalizador Linear de Tempo Contínuo"), bem como um DFE (Decision Feedback Equalizer, ou "Equalização por Feedback de Decisão").

Tabela 5 - Sistemas de equalização de sinais implementados no PCIe a partir da rev. 3.0

A combinação de equalização no transmissor e no receptor em um lane de dados serial de alta velocidade permite que os projetos atinjam mais de 28 Gbits/s. Uma conexão PCIe 5.0 x1 já ultrapassa tal valor (3,938 MB = aprox. 31,2 Gbit). A equalização continuará a desempenhar um papel fundamental à medida que migramos da modulação NRZ (unipolar de dois níveis sem retorno a zero) para PAM4 (modulação de amplitude de pulso de quatro níveis) com taxas superiores a 50 Gbits/s.

Acoplamento de circuitos

Note a existência de um capacitor de acoplamento (AC Coupling Capacitor).

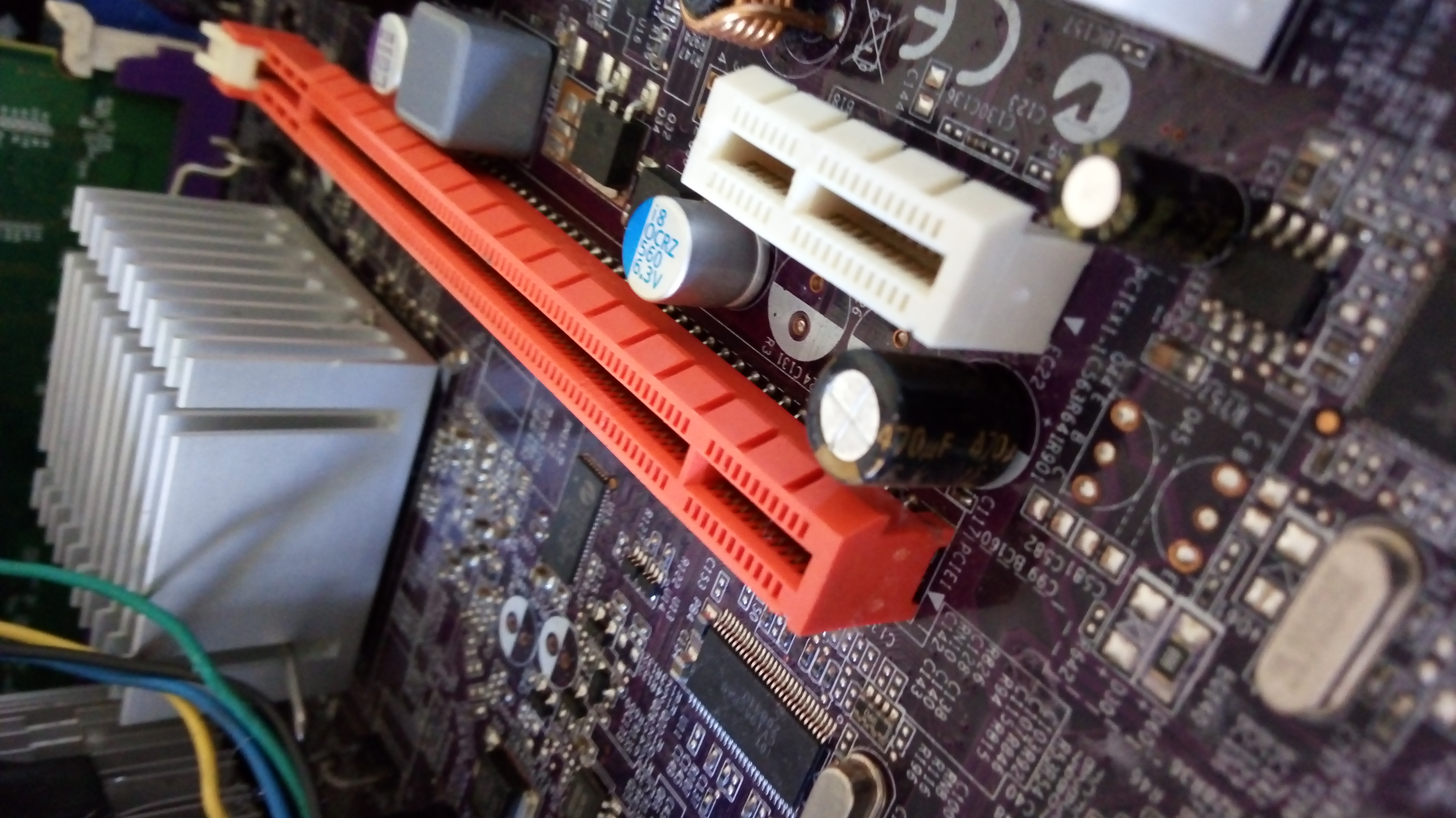

Se você já observou uma placa-mãe, viu que logo acima do slot PCIe há alguns componentes SMD. Veja a imagem abaixo para entender melhor:

Imagem 7 - Placa-mãe Gigabyte GA-8i915G MF

Os componentes circulados em amarelo são capacitores SMD, pequenas peças que fazem uma simples filtragem no sinal transmitido pelas trilhas TX dos lanes, isto é, são capacitores de acoplamento, que tem como propósito bloquear a corrente contínua (CC), deixando acorrente alternada (AC) ou pulsante (no caso de eletrônica digital) passar.

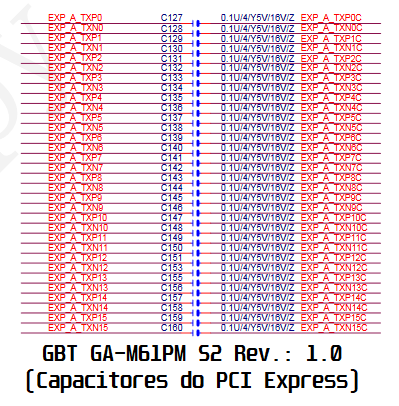

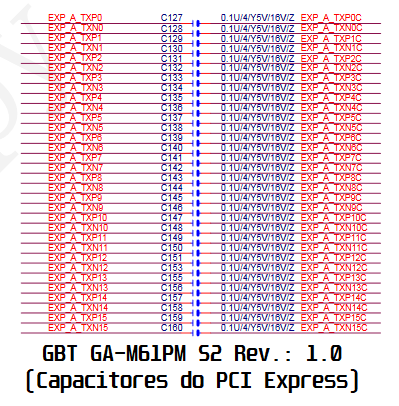

Abaixo, você vê o diagrama de duas placas-mãe, também da marca Gigabyte, mostrando a posição e a numeração destes capacitores no circuito do slot PCIe. Observe:

Esquema elétrico da GBT GA-M59SLI S4 Ver.: 1.00

Esquema elétrico da GBT GA-M61PM S2 Ver.: 1.00

Estes capacitores possuem características padronizadas, sendo que a capacitância que é sempre na faixa dos 0,1 microFarad.

Outro detalhe é que, se você viu bem os dois diagramas, apenas as trilhas de TX (Transceiver) possuem capacitores SMD, as trilhas RX (Receiver) não possuem capacitores. Mas qual o motivo?

A placa que será conectada ao slot virá com os capacitores de acoplamento SMD para RX. Pode analisar uma placa de vídeo ou qualquer outra placa compatível com PCIe. Todas elas vem com capacitores das linhas RX próximos dos contatos do conector!

Observe as imagens abaixo:

Imagem 8 - Placa de vídeo EVGA nVidia GT730 (interface PCIe x8)

Imagem 9 - Placa de vídeo GeForce 6200CT (interface PCIe x16)

Lembrando que, estes capacitores nas linhas TX e RX dos lanes são organizados desta forma em todas as placas-mãe e todos os circuitos que podem ser conectados ao PCIe, ou seja, placas de áudio, vídeo, rede, captura, SSDs, entre várias outras. Capacitores das linhas RX também trabalham na mesma faixa de capacitância dos capacitores para as linhas TX.

O que foi dito no parágrafo anterior também vale para outros formatos de slot que tenham linhas PCIe, como é o caso do M.2. Note os capacitores nas linhas RX deste SSD:

Imagem 10 - SSD NVMe comparado com um cartão SD. Note os capacitores de acoplamento dos quatro pares de cancelamento RX

E quem diria que o textinho lançado em 2018 chegasse nesse nível. Esperamos um dia lançar o Capítulo 4, e creio que logo virá, afinal o PCIe 6.0 já teve suas especs lançadas em 2022, utilizando modulação PAM (ao invés da NRZ) e já foi dada a largada para a criação do PCIe 7.0, com expectativa de lançamento para meados de 2025.

Para acessar o Capítulo 2, CLIQUE AQUI!

Para acessar o Capítulo 3, CLIQUE AQUI!

O que achou do artigo? Faltou alguma coisa? Ficou com alguma dúvida?

Mande suas dúvidas, sugestões e reclamações para hardwarecentrallr@gmail.com.

Não se esqueça de curtir, comentar e compartilhar! Ajude a divulgar o site!

REFERÊNCIAS e CRÉDITOS

Fotos, diagramas, texto e animação: Leonardo Ritter

Referências: Livro de Redes de computadores de Gabriel Torres (codificação 8B/10B); Guia do Hardware; Clube do Hardware; Pinouts.ru; Biblioteca de diagramas do Hardware Central; Wikipedia (somente artigos com fontes verificadas!); Trabalho de engenharia reversa feito pelo autor deste texto.

Última atualização: 06 de Janeiro de 2023.